基于Proteus的RAM扩展实验

1.掌握RAM存储器存储容量扩展的工作原理;

2.掌握RAM存储器存储容量扩展时与CPU的连接方法;

3.掌握RAM芯片在扩展后写入数据和读出数据的方法和操作过程。

使用RAM芯片进行容量扩展,并实现数据的写入和读出操作。

具体要求是:假设计算机系统有16根地址总线,8根数据总线。请用8K×8位的RAM芯片构建16K×8位的内存系统,地址空间为0~16K-1。画出仿真电路图,并完成对1K和16K-1两个地址单元内数据的读写操作。

单片存储芯片的容量是有限的,很难满足一个计算机系统对大存储容量的需求,因此在某些场合下需要将若干个存储芯片连接在一起才能构建一个大容量的存储系统,这个过程称为存储容量的扩展。扩展方法通常有字扩展、位扩展和字位混合扩展三种方法。

字扩展是指增加存储字的数量。例如,用2K×8位的6116芯片构建8K×8位的内存系统,就是字扩展。

位扩展是指增加存储字长。例如,用1K×4位的2114芯片构建lK×8位的内存系统,就是位扩展。

字位混合扩展是指既增加存储字的容量,又增加存储字长。例如,用1K×4位的2114芯片构建2K×8位的内存系统,就是字位混合扩展。

本实验要用8K×8位的RAM芯片构建16K×8位的内存系统,属于字扩展。

四、实验方法

模块化教学法:教师引导学生对实验任务进行分解,将任务按照功能划分为多个子模块;学生对各个子模块进行详细的设计,最后整合成完整的仿真电路图。

任务驱动教学法:学生针对各个模块的功能进行探究,分析为了完成模块的功能,都需要使用什么器件,研究器件的工作原理、使用方法以及器件之间如何相互连接等问题,完成各个模块的仿真电路图;教师可以辅助引导,并检查学生对各个模块进行测试的过程和结果。

五、仿真电路图的设计过程

1、对仿真电路图进行总体设计,划分功能子模块

若想实现对RAM 的读写操作,首先需要为RAM提供一个地址,经过译码,选中RAM一个存储单元,然后在写信号的控制下,通过数据总线向该RAM单元写数据,最后在读信号的控制下,将该单元的数据读出。由此得出,本实验的仿真电路应该包括以下子模块:

地址总线输出模块:输出访问RAM的地址,并显示在地址通路的数码管上;

RAM地址输入仿真模块:地址总线上的地址经过锁存器的锁存,分成两部分,低位地址直接与RAM内部的地址引脚相连,高位地址送入译码器译码;

数据总线输出模块:输出要写到RAM单元的数据,并显示在数据通路的数码管上;

RAM数据输入/输出模块:将RAM内部的数据引脚直接连接到数据总线上即可,数据会立即显示在数据通路的数码管上;

片选信号生成模块:高位地址送入译码器译码,生成的信号就是RAM芯片的片选信号;

控制信号仿真模块:电路中所有的控制信号都由单刀双掷开关实现。

2、确定仿真电路图所需元器件

地址总线输出模块和数据总线输出模块都由上拉电阻、拨码开关、三态门和数码管构成。RAM芯片的容量是8K×8位,选择6264芯片。地址总线的低位经74LS273锁存器输入到RAM,高位上没用到的地址总线经74LS138译码器译码后生成RAM芯片的片选信号。RAM芯片的数据输出直接连数据总线。综上所述,可得本实验的原件清单表,如表1所示。各仿真原件图如图1所示。

表1 本实验元器件清单

序号 |

元器件型号 |

元器件名称 |

简单描述 |

1 |

RESPACK-8 |

8位排阻 |

1号引脚接+5V,2~9号引脚为I/O引脚 |

2 |

DIPSWC_8 |

8位拨码开关 |

9号引脚接GND,1~8号引脚为I/O引脚 |

3 |

74LS244 |

三态门 |

A3~A0、Y3~Y0为I、O引脚,  为数据输出使能端,低电平有效 为数据输出使能端,低电平有效

|

4 |

7SEG-BCD-GRN |

4位BCD码显示管 |

以十六进制显示4位二进制 |

5 |

74LS273 |

8位锁存器 |

MR引脚高电平有效,D7~D0为数据输入端,Q7~Q0为数据输出端,CLK引脚上升沿有效 |

6 |

74LS138 |

3-8译码器 |

E1、E2、E3为使能端,E1高有效,E2和E3低有效,CBA是地址输入端,Y7~Y0为译码输出端,输出的有效信号为低电平 |

7 |

6264 |

RAM芯片 |

容量为8K×8位,A12~A0为地址输入引脚, D7~D0为数据I/O引脚。 为低电平有效的片选信号,CS为高电平有效的片选信号。 为低电平有效的片选信号,CS为高电平有效的片选信号。 和 和 分别为写信号和读信号,低电平有效 分别为写信号和读信号,低电平有效 |

8 |

SW-SPDT |

单刀双掷开关 |

双端为动端,可分别接高、低电平。单端为不动端,是电平输出引脚 |

图1 仿真原件图

3、地址总线输出通路仿真

由于地址总线有16根,所以需要两组排阻和拨码开关电路、4个74LS244三态门、4个数码管。在 开关有效(低电平)的前提下,16位地址会输出到地址总线并显示在数码管上。

开关有效(低电平)的前提下,16位地址会输出到地址总线并显示在数码管上。

图2 地址总线输出仿真电路图

4、RAM地址输入仿真

由于6264芯片的容量是8K×8位,则构建16K×8位的内存系统需要2片6264,而8K=213,所以每片6264内部的地址引脚有13根。地址总线上的16位地址经74LS273锁存后,低13位接入RAM芯片。74LS273芯片上午MR引脚接+5V,CLK引脚是上升沿有效,所以需要由控制开关进行控制。

图3 RAM地址输入仿真电路图

5、数据总线输出通路仿真

由于数据总线有8根,所以需要1组排阻和拨码开关电路、2个74LS244三态门、2个数码管。在 开关有效(低电平)的前提下,8位数据会输出到数据总线并显示在数码管上。

开关有效(低电平)的前提下,8位数据会输出到数据总线并显示在数码管上。

图4 数据总线输出仿真电路图

6、RAM数据输入/输出仿真

将两片6264芯片的数据引脚D7~D0直接连到数据总线上即可。

图5 RAM数据输入/输出仿真电路图

7、RAM片选信号 和读、写信号仿真

和读、写信号仿真

由于本实验的容量扩展属于字扩展,所以两个芯片是分时被选中的,则两个芯片的片选逻辑不相同,而且需要根据实验要求的地址空间确定每个芯片片选信号 的具体实现。方法如下:

的具体实现。方法如下:

首先将内存地址空间的首、尾地址转换成16位二进制:

0:0000 0000 0000 0000

16K-1:0011 1111 1111 1111

然后根据地址高三位的值确定译码器的译码结果:观察首、尾地址的二进制值可知,地址的高三位有两种情况,分别是:000、001,所以要用Y0、Y1控制两片6264的片选信号 。

。

RAM的读、写信号都由控制开关进行控制。

图6 RAM片选信号及读写信号仿真电路图

8、控制信号仿真

本实验设计的控制信号共有五个,都由单刀双掷开关实现。

图7 控制开关仿真电路图

1、将所有开关置为1,然后启动仿真;

2、置 =0,手动拨码开关,向地址总线写入一个有效的地址,显示在地址通路的数码管上;

=0,手动拨码开关,向地址总线写入一个有效的地址,显示在地址通路的数码管上;

3、置RAM_CLK=0后再置RAM_CLK=1,使锁存器74LS273的CLK引脚获得一个上升沿,将地址总线上的A15~A0打入锁存器74LS273。74LS273将锁存到的数据直接输出,所以A15~A0直通74LS138和6264,在6264芯片中,由A12~A0指向的地址单元被选中;

4、RAM写操作:置 =0,手动拨码开关,向数据总线写入一个数据,显示在数据通路的数码管上。置

=0,手动拨码开关,向数据总线写入一个数据,显示在数据通路的数码管上。置 =0,将该数据写入到6264被选中的存储单元;

=0,将该数据写入到6264被选中的存储单元;

5、RAM读操作:置 =1,关闭写6264操作。置

=1,关闭写6264操作。置 =1,关闭拨码开关至数据总线的数据输出。置

=1,关闭拨码开关至数据总线的数据输出。置 =0,则6264被选中的存储单元中存储的数据将输出至数据数据总线,且显示在数据通路的数码管上。

=0,则6264被选中的存储单元中存储的数据将输出至数据数据总线,且显示在数据通路的数码管上。

学生对整个实验的完成过程进行描述,内容包括实验的完成思路、设计方法、仿真操作步骤以及实验过程中遇到的问题和解决办法等。教师可以在学生描述的过程中对学生进行提问,也可以给学生提出一些思考题并检查学生的完成情况。思考题举例如下:

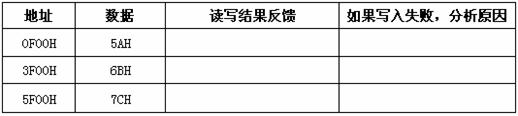

表2 字扩展数据表

1、将表2中的数据写入对应的地址下,并逐一读出;

2、若将地址范围改为32K~48K-1,则仿真电路图需怎么修改?

3、若将74LS138译码器的输出端改成/Y6/、Y7,那么会对整个内存系统有什么影响?

八、考核方法

考核方法注重过程化以及学生独立解决问题的能力,对本实验的考核阶段及比重划分如下:

1、功能子模块划分及仿真电路图的完成情况占比30%;

2、RAM读写操作过程及仿真结果占比30%;

3、学生答辩占比30%;

4、实验报告占比10%。